淺談嵌入式MCU硬件設計之MCU最小系統(tǒng)電路與集成電路設計

在嵌入式系統(tǒng)開發(fā)領域,微控制器(MCU)是核心與靈魂。一個穩(wěn)定、可靠的嵌入式硬件平臺始于MCU最小系統(tǒng)電路的正確設計。作為其物理載體的集成電路(IC)設計理念,也深刻影響著MCU的選型與應用。本文將探討MCU最小系統(tǒng)電路的關鍵組成部分,并簡述其與更宏觀的集成電路設計思想之間的聯(lián)系。

一、MCU最小系統(tǒng)電路:嵌入式硬件的基礎

MCU最小系統(tǒng),是指微控制器能夠獨立運行程序所必需的最基本外圍電路。它確保了MCU在上電后能正確初始化、執(zhí)行代碼。一個典型的最小系統(tǒng)通常包含以下幾個核心部分:

- 電源電路:為MCU提供穩(wěn)定、潔凈的直流工作電壓。設計時需注意電壓等級(如3.3V、5V)、功耗估算,并必須加入去耦電容(通常為0.1μF的陶瓷電容靠近電源引腳放置),以濾除高頻噪聲,確保內核及I/O電源的穩(wěn)定性。

- 復位電路:確保MCU在上電或異常時能可靠地恢復到已知的初始狀態(tài)。主要有上電復位(通過RC電路實現(xiàn)簡單延時)和手動復位兩種。許多現(xiàn)代MCU也集成了內部復位源,但外部復位電路對于提高系統(tǒng)在惡劣環(huán)境下的可靠性仍至關重要。

- 時鐘電路:為MCU提供工作節(jié)拍。可分為外部時鐘(有源晶振)和內部時鐘(RC振蕩器)兩種方式。對于需要高精度定時、通信(如USB、UART)的應用,外部晶振搭配負載電容構成的諧振電路是標準選擇,其布局布線需遠離噪聲源且路徑盡量短。內部時鐘則節(jié)省成本與空間,適用于時序要求不嚴的場合。

- 啟動配置電路:通過設置特定的引腳電平(如BOOT0, BOOT1),決定MCU從上電后從何處開始執(zhí)行代碼(如系統(tǒng)存儲器、內置Flash或SRAM)。正確的配置是程序能否加載運行的前提。

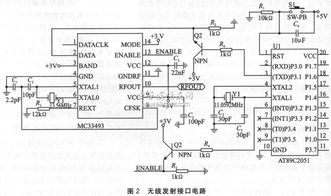

- 調試/下載接口:如JTAG、SWD等,用于程序燒錄與在線調試。這是開發(fā)階段必不可少的橋梁,設計時需注意接口信號線的上拉/下拉電阻配置及走線。

二、最小系統(tǒng)設計中的集成電路設計思想

MCU本身就是一個高度集成的片上系統(tǒng)(SoC)。其內部集成了CPU內核、存儲器、定時器、多種外設接口等。因此,在規(guī)劃最小系統(tǒng)時,實質上是在進行一次“系統(tǒng)級”的集成電路應用設計:

- 選型與資源評估:如同IC設計中的規(guī)格定義,需根據(jù)應用需求(性能、功耗、外設、成本)選擇合適的MCU型號,評估其內部資源(Flash、RAM、GPIO數(shù)量等)是否滿足要求,這直接決定了后續(xù)電路和軟件的復雜度。

- 引腳復用與功能分配:現(xiàn)代MCU引腳普遍具有復用功能。硬件設計時需仔細查閱數(shù)據(jù)手冊,合理分配引腳功能(如GPIO、ADC、通信接口),避免沖突,并考慮未使用引腳的處理方式(如上拉/下拉或配置為輸出),以優(yōu)化功耗與抗干擾性。

- 信號完整性考慮:盡管是板級設計,但高速信號(如外部存儲器總線、高頻時鐘)的走線需要遵循基本的IC互連設計原則,如阻抗匹配、減少過孔、避免銳角走線,以保障信號質量。

- 電源完整性管理:MCU內部不同模塊(模擬、數(shù)字、I/O)通常需要獨立的電源域或濾波。最小系統(tǒng)設計中的電源網(wǎng)絡布局(如使用星型拓撲、大面積鋪地)直接反映了對芯片內部供電網(wǎng)絡穩(wěn)定性的支持。

- ESD與可靠性設計:在接口電路上增加ESD保護器件、TVS管等,是對MCU內部脆弱CMOS電路的必要保護,體現(xiàn)了從芯片到系統(tǒng)的可靠性延伸設計。

三、

MCU最小系統(tǒng)電路設計,是嵌入式硬件工程師將一顆高度集成的硅片轉化為一個可控、可用的智能節(jié)點的第一步。它既是嚴謹?shù)碾娮庸こ虒嵺`,也處處滲透著集成電路設計的系統(tǒng)思維——從芯片內部結構的理解,到外部資源的合理配置與優(yōu)化。一個優(yōu)秀的最小系統(tǒng)設計,不僅追求“能工作”,更追求在穩(wěn)定性、抗干擾、可生產性及成本上的平衡,為整個嵌入式產品的成功奠定堅實的硬件基石。隨著MCU集成度越來越高(集成DC-DC、射頻、安全模塊等),最小系統(tǒng)的外圍電路可能會簡化,但對設計者理解芯片內部架構、數(shù)據(jù)手冊以及系統(tǒng)級設計能力的要求卻愈發(fā)提高。

如若轉載,請注明出處:http://www.lazbw.cn/product/51.html

更新時間:2026-01-07 18:34:47