一文看懂半導(dǎo)體芯片產(chǎn)業(yè)鏈 聚焦上游核心環(huán)節(jié)——集成電路設(shè)計(jì)

半導(dǎo)體芯片是現(xiàn)代電子工業(yè)的基石,其產(chǎn)業(yè)鏈復(fù)雜且高度專業(yè)化,通常被劃分為上游、中游和下游三大環(huán)節(jié)。其中,上游的集成電路設(shè)計(jì)是整個(gè)產(chǎn)業(yè)的源頭與創(chuàng)新引擎,決定了芯片的性能、功能與市場(chǎng)競(jìng)爭(zhēng)力。

產(chǎn)業(yè)鏈全景概述

在深入探討設(shè)計(jì)環(huán)節(jié)之前,我們首先俯瞰整個(gè)產(chǎn)業(yè)鏈的脈絡(luò):

- 上游(芯片誕生前):主要包括集成電路設(shè)計(jì)與核心IP、EDA工具及材料設(shè)備的支撐環(huán)節(jié)。這是知識(shí)和技術(shù)最密集的領(lǐng)域。

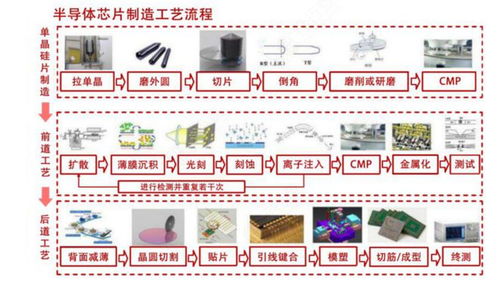

- 中游(芯片制造中):核心是晶圓制造與封裝測(cè)試,即將設(shè)計(jì)好的圖紙轉(zhuǎn)化為實(shí)體芯片的物理實(shí)現(xiàn)過程,資本和技術(shù)壁壘極高。

- 下游(芯片應(yīng)用端):涉及各類芯片產(chǎn)品(如CPU、存儲(chǔ)器)的銷售,以及將其集成到系統(tǒng)廠商(如手機(jī)、電腦、汽車制造商)的終端產(chǎn)品中,最終抵達(dá)消費(fèi)者。

整個(gè)鏈條環(huán)環(huán)相扣,而集成電路設(shè)計(jì)作為邏輯起點(diǎn),其重要性不言而喻。

核心聚焦:集成電路設(shè)計(jì)

集成電路設(shè)計(jì),常被稱為IC設(shè)計(jì)或芯片設(shè)計(jì),位于產(chǎn)業(yè)鏈最上游。其本質(zhì)是根據(jù)終端應(yīng)用需求,利用電子設(shè)計(jì)自動(dòng)化(EDA)工具,進(jìn)行邏輯與電路設(shè)計(jì),最終輸出可供制造的芯片版圖(類似于建筑的“藍(lán)圖紙”)。

1. 設(shè)計(jì)流程與關(guān)鍵步驟

- 需求定義與規(guī)格制定:與客戶或市場(chǎng)部門溝通,明確芯片的功能、性能、功耗、成本等目標(biāo)。這是所有工作的基礎(chǔ)。

- 架構(gòu)設(shè)計(jì):進(jìn)行高層次規(guī)劃,確定芯片的整體架構(gòu)、模塊劃分以及核心算法(如CPU的流水線設(shè)計(jì)、AI芯片的神經(jīng)網(wǎng)絡(luò)加速器設(shè)計(jì))。

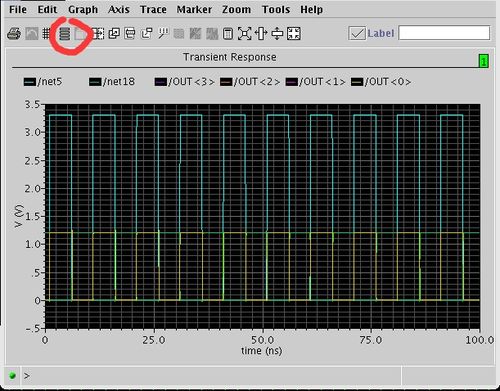

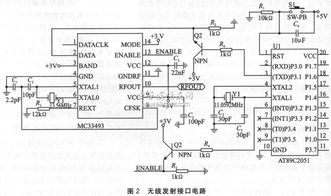

- 邏輯設(shè)計(jì)與驗(yàn)證:使用硬件描述語言(如Verilog、VHDL)編寫代碼,描述芯片各模塊的邏輯功能,并通過仿真進(jìn)行嚴(yán)格驗(yàn)證,確保邏輯正確。

- 物理設(shè)計(jì):將邏輯電路轉(zhuǎn)化為實(shí)際的物理版圖,包括布局(確定元件位置)、布線(連接所有元件)、時(shí)序與功耗分析等。這是設(shè)計(jì)與制造的橋梁。

- 交付與流片:將最終確認(rèn)的版圖數(shù)據(jù)(GDSII格式)交付給晶圓代工廠(Foundry),進(jìn)行首次試生產(chǎn),即“流片”。流片成功是設(shè)計(jì)環(huán)節(jié)完成的標(biāo)志。

2. 設(shè)計(jì)模式與主要參與者

- Fabless模式(無晶圓廠設(shè)計(jì)公司):這是當(dāng)今主流模式。公司只專注于芯片設(shè)計(jì),將制造、封裝測(cè)試外包給專業(yè)代工廠。例如高通(Qualcomm)、英偉達(dá)(NVIDIA)、華為海思、聯(lián)發(fā)科(MediaTek)等巨頭均采用此模式。它們輕資產(chǎn)運(yùn)營(yíng),核心競(jìng)爭(zhēng)力在于創(chuàng)新、設(shè)計(jì)與IP積累。

- IDM模式(垂直整合制造):公司業(yè)務(wù)覆蓋設(shè)計(jì)、制造、封測(cè)全鏈條。如英特爾(Intel)、三星(Samsung)、德州儀器(TI)。此模式資源整合度高,但資本投入巨大。

- 設(shè)計(jì)服務(wù)與IP授權(quán)商:如ARM公司,不生產(chǎn)芯片,而是通過授權(quán)其處理器架構(gòu)等核心知識(shí)產(chǎn)權(quán)(IP)給設(shè)計(jì)公司獲利,是生態(tài)中的重要支撐。

3. 設(shè)計(jì)的核心支撐要素

- EDA工具:芯片設(shè)計(jì)的“畫筆”和“仿真實(shí)驗(yàn)室”。全球市場(chǎng)主要由新思科技(Synopsys)、鏗騰電子(Cadence)、西門子EDA(原Mentor Graphics)三大巨頭壟斷。沒有先進(jìn)的EDA工具,復(fù)雜芯片設(shè)計(jì)寸步難行。

- 半導(dǎo)體IP核:預(yù)先設(shè)計(jì)好的、經(jīng)過驗(yàn)證的、可重復(fù)使用的功能模塊(如CPU核、接口協(xié)議IP)。使用IP核能大幅縮短設(shè)計(jì)周期,降低研發(fā)風(fēng)險(xiǎn)和成本。

- 專業(yè)人才:需要跨學(xué)科的頂尖工程師團(tuán)隊(duì),精通體系結(jié)構(gòu)、微電子、計(jì)算機(jī)、算法等多個(gè)領(lǐng)域。

設(shè)計(jì)環(huán)節(jié)的挑戰(zhàn)與趨勢(shì)

- 技術(shù)挑戰(zhàn):隨著工藝節(jié)點(diǎn)向3納米、2納米邁進(jìn),設(shè)計(jì)復(fù)雜度呈指數(shù)級(jí)增長(zhǎng),功耗、散熱、信號(hào)完整性等問題日益嚴(yán)峻。

- 高投入與高風(fēng)險(xiǎn):先進(jìn)工藝芯片設(shè)計(jì)成本動(dòng)輒數(shù)億美元,且流片失敗風(fēng)險(xiǎn)巨大,對(duì)公司的資金和技術(shù)實(shí)力是終極考驗(yàn)。

- 未來趨勢(shì):

- 異構(gòu)集成與Chiplet(芯粒):通過將不同工藝、功能的模塊化芯片封裝在一起,提升性能并降低成本,正在改變傳統(tǒng)設(shè)計(jì)范式。

- 領(lǐng)域?qū)S眉軜?gòu):針對(duì)AI、自動(dòng)駕駛、數(shù)據(jù)中心等特定場(chǎng)景,設(shè)計(jì)專用芯片(如DPU、NPU),以獲取更高的能效比。

- 全產(chǎn)業(yè)鏈協(xié)同:設(shè)計(jì)與制造(DTCO)、設(shè)計(jì)與封裝(STCO)的協(xié)同優(yōu)化愈發(fā)重要,要求設(shè)計(jì)公司更深入地理解中下游工藝。

###

集成電路設(shè)計(jì)是半導(dǎo)體產(chǎn)業(yè)鏈的“大腦”與“藍(lán)圖繪制者”,它將抽象的創(chuàng)意與應(yīng)用需求,轉(zhuǎn)化為精密復(fù)雜的物理現(xiàn)實(shí)。理解設(shè)計(jì)環(huán)節(jié),是理解芯片如何誕生、以及為何高端芯片研發(fā)如此艱難的關(guān)鍵第一步。在全球化與科技競(jìng)爭(zhēng)背景下,強(qiáng)大的芯片設(shè)計(jì)能力已成為國(guó)家科技實(shí)力的重要標(biāo)志,持續(xù)驅(qū)動(dòng)著下游整個(gè)電子信息產(chǎn)業(yè)的創(chuàng)新與變革。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.lazbw.cn/product/47.html

更新時(shí)間:2026-01-05 20:30:04