超大規(guī)模集成電路設(shè)計(jì)中的MOS器件原理(三)與集成電路設(shè)計(jì)

超大規(guī)模集成電路(VLSI)設(shè)計(jì)是現(xiàn)代電子技術(shù)的核心,而金屬氧化物半導(dǎo)體(MOS)器件作為其基本構(gòu)建單元,其原理理解至關(guān)重要。本文是系列文章的第三部分,將深入探討MOS器件原理及其在集成電路設(shè)計(jì)中的應(yīng)用,涵蓋器件特性、設(shè)計(jì)挑戰(zhàn)以及實(shí)際優(yōu)化策略。

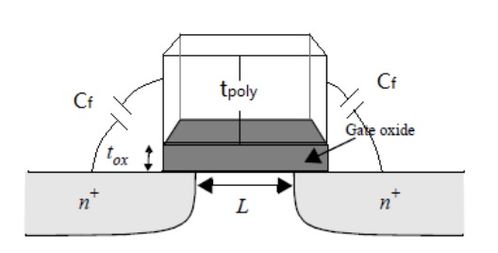

MOS器件的基本原理基于場(chǎng)效應(yīng)晶體管(FET)結(jié)構(gòu),包括源極、漏極、柵極和襯底。當(dāng)柵極施加電壓時(shí),會(huì)在半導(dǎo)體表面形成導(dǎo)電溝道,從而控制電流從源極流向漏極。這種開(kāi)關(guān)行為是數(shù)字電路的基礎(chǔ),例如在邏輯門(mén)中實(shí)現(xiàn)二進(jìn)制操作。在超大規(guī)模集成電路中,MOS器件的尺寸不斷縮小,遵循摩爾定律,這帶來(lái)了更高的集成度和性能,但也引入了短溝道效應(yīng)、漏電流增加和功耗問(wèn)題。因此,設(shè)計(jì)時(shí)必須考慮器件縮放極限,并采用多閾值電壓技術(shù)或高介電常數(shù)材料來(lái)優(yōu)化性能。

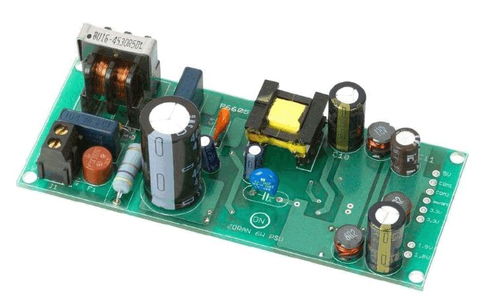

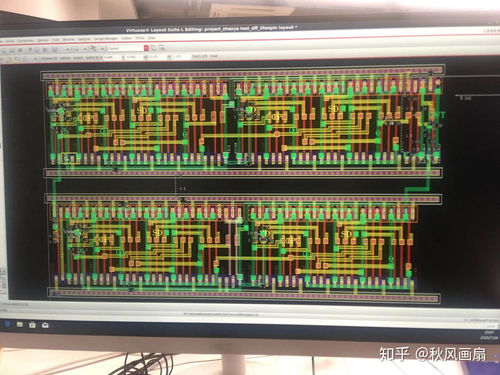

在集成電路設(shè)計(jì)中,MOS器件的原理直接應(yīng)用于電路布局和時(shí)序分析。例如,在CMOS(互補(bǔ)MOS)技術(shù)中,結(jié)合NMOS和PMOS器件,可以實(shí)現(xiàn)低功耗和高噪聲容限的邏輯電路。設(shè)計(jì)流程包括前端設(shè)計(jì)(如邏輯綜合)和后端設(shè)計(jì)(如物理布局),其中MOS器件的參數(shù)(如閾值電壓和跨導(dǎo))會(huì)影響電路的速度和功耗。隨著工藝節(jié)點(diǎn)向納米級(jí)演進(jìn),設(shè)計(jì)者需應(yīng)對(duì)寄生效應(yīng)和熱管理挑戰(zhàn),采用EDA工具進(jìn)行仿真和驗(yàn)證。

掌握MOS器件原理是超大規(guī)模集成電路設(shè)計(jì)的關(guān)鍵,它不僅驅(qū)動(dòng)了技術(shù)進(jìn)步,還推動(dòng)了從微處理器到存儲(chǔ)芯片的廣泛應(yīng)用。隨著新材料如FinFET和GAA晶體管的引入,設(shè)計(jì)者將繼續(xù)優(yōu)化器件性能,以滿足人工智能和物聯(lián)網(wǎng)等新興領(lǐng)域的需求。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.lazbw.cn/product/27.html

更新時(shí)間:2026-01-07 23:17:08