精密的處理器 集成電路設計中的藝術與科學

在當今數字時代的核心,處理器以其令人驚嘆的精密性驅動著從智能手機到超級計算機的每一臺智能設備。這種精密性并非偶然,而是集成電路設計這門融合了藝術與科學的尖端學科所成就的杰作。

一、 設計的起點:架構與指令集

處理器的精密之旅始于頂層設計。架構師們需要做出根本性決策:是采用精簡指令集(RISC)還是復雜指令集(CISC)?如何設計核心微架構以實現性能、功耗和芯片面積的完美平衡?現代處理器,如多核、眾核架構,甚至引入了異構計算單元(如CPU+GPU+NPU),其設計復雜度呈指數級增長。指令集架構(ISA)作為硬件與軟件之間的契約,定義了處理器的“語言”,其設計的優雅與高效直接決定了后續所有設計環節的上限。

二、 邏輯實現:從抽象到電路

一旦架構確定,設計便進入邏輯實現階段。工程師們使用硬件描述語言(如Verilog或VHDL),將處理器的功能(如加法器、緩存控制器、分支預測器)描述為寄存器傳輸級(RTL)代碼。這一過程如同用代碼“雕刻”出處理器的靈魂。通過邏輯綜合工具,這些RTL描述被自動轉化為由基本邏輯門(如與門、或門、非門)組成的網表。此時,設計從抽象的行為描述,邁向了具體的電路結構。

三、 物理設計:在納米尺度上布局布線

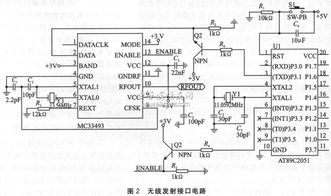

這是精密性體現得最為淋漓盡致的階段。物理設計的目標是將邏輯網表轉化為可用于制造的幾何圖形(版圖)。

- 布局:數十億個晶體管需要被合理地放置在芯片的二維平面上。關鍵路徑上的元件必須靠近以降低延遲,而發熱單元則需要分散以避免局部過熱。這如同在微觀世界里規劃一座超級大都市,既要保證“交通”(信號)流暢,又要確保“居民”(晶體管)安居。

- 布線:在晶體管之間鋪設連接它們的金屬導線。在納米工藝下,導線本身的電阻和電容成為影響信號速度與功耗的主要因素。設計者必須進行精密的時序分析、信號完整性分析和功耗分析,反復迭代,確保每一條信號都能在要求的時間內、以足夠的強度到達目的地,且避免串擾和噪聲。

- 設計規則檢查:必須嚴格遵守晶圓廠提供的數百條物理設計規則,確保版圖能夠被成功制造。任何微小的違規都可能導致芯片失效。

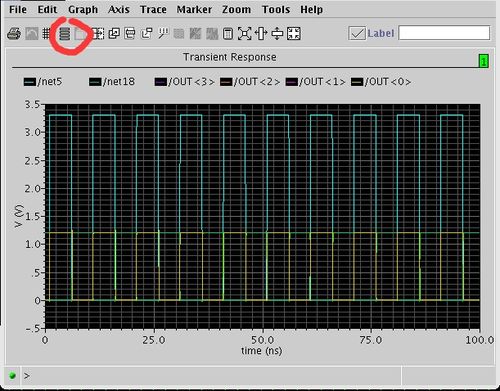

四、 驗證與仿真:確保萬無一失

在投入數十億美元進行流片制造之前,驗證是確保設計正確的最后、也是最重要的關卡。工程師們構建龐大的測試平臺,運行數百萬甚至數十億個測試向量,模擬處理器在各種極端和正常情況下的行為。形式驗證工具則從數學上證明設計的某些屬性絕對正確。隨著芯片復雜度提升,驗證工作所占用的時間和資源往往超過設計本身。

五、 先進技術與未來挑戰

現代處理器設計正不斷逼近物理極限:

- 先進工藝:從7納米、5納米到3納米乃至更小,晶體管尺寸的微縮帶來了性能提升和功耗降低,但也使得漏電、工藝變異和制造復雜性劇增。

- 新器件與新材料:為了延續摩爾定律,業界正在探索環柵晶體管(GAA)、碳納米管、二維材料等全新路徑。

- 系統級協同設計:處理器不再是孤立的芯片,而是與封裝技術(如2.5D/3D集成)、內存(如HBM)、高速接口等緊密結合。芯片級(Chiplet)設計通過將大芯片分解為多個小芯片集成,成為提升良率和設計靈活性的關鍵。

- 專用領域架構:為人工智能、圖形處理、網絡處理等特定任務設計高度定制化的處理器核心,以達成極致的能效比,這正成為創新的熱點。

精密的處理器是現代人類智慧的結晶。集成電路設計是一個不斷在性能、功耗、面積、成本和開發時間之間進行精妙權衡的旅程。它既需要嚴謹的數學、物理和工程學基礎,也需要創造性的思維來解決前所未有的挑戰。隨著我們步入萬物智能互聯的時代,對更強大、更高效、更智能的處理器的需求永無止境,而這門精密的藝術與科學,也必將繼續推動著人類技術前沿的不斷突破。

如若轉載,請注明出處:http://www.lazbw.cn/product/35.html

更新時間:2026-01-05 04:11:17