集成電路封裝 設計完成后的關鍵環節

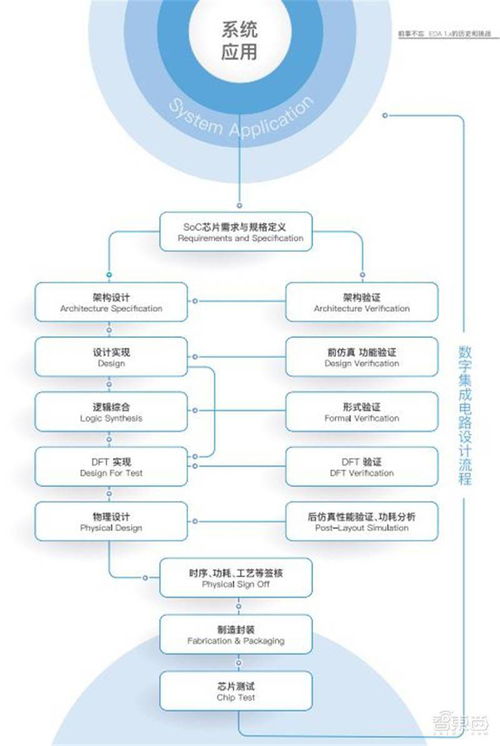

集成電路(Integrated Circuit, IC)是現代電子技術的核心,其完整的生命周期主要包括兩大關鍵階段:集成電路設計和集成電路封裝。設計環節決定了芯片的功能與性能,而封裝環節則負責將設計好的裸片(Die)進行物理保護、電氣連接、信號傳輸、散熱管理,并最終形成一個可在實際系統中穩定工作的獨立器件。本文將對集成電路封裝進行概述,并闡明其與集成電路設計的緊密關系。

一、 集成電路封裝的核心作用與定義

集成電路封裝是指利用特定的材料(如陶瓷、塑料、金屬)和工藝,將經過制造、測試合格的半導體晶圓上切割下來的獨立裸片,安置在封裝基板或引線框架上,并通過鍵合(如引線鍵合、倒裝芯片)等方式實現裸片與外部引腳的電性連接,最后加以密封保護,形成具有標準外形尺寸和接口的成品芯片的過程。

其主要作用可歸納為以下幾點:

- 物理保護:脆弱的硅裸片極易受到機械損傷、灰塵污染及潮濕、化學物質的侵蝕。封裝為其提供了一個堅固的外殼,確保其在運輸、安裝和使用過程中的可靠性。

- 電氣連接:將裸片上微米級的電路接點,通過內部互連技術(如金線、銅柱)擴展到封裝外部的毫米級引腳,從而方便與印刷電路板(PCB)進行焊接和連接,構成完整的電子系統。

- 散熱管理:芯片在工作時會產生熱量,若熱量積聚會導致性能下降甚至失效。封裝結構和材料(如散熱蓋、導熱膠)是耗散這些熱量的關鍵路徑。

- 信號完整性:隨著工作頻率的提高,封裝內部的寄生電感和電容會嚴重影響信號質量。先進的封裝設計致力于優化信號傳輸路徑,減少延遲、反射和串擾。

- 標準化與小型化:封裝提供了標準化的外形和引腳排列,便于系統集成。封裝技術本身也在不斷追求更小的體積、更高的引腳密度(如芯片級封裝CSP、晶圓級封裝WLP),以順應電子產品輕薄短小的趨勢。

二、 封裝與設計的共生關系

集成電路封裝并非一個獨立于設計的后續工序,而是與芯片設計深度耦合、協同優化的過程。這種關系體現在:

- 設計階段的封裝選型與協同設計:在芯片設計初期,就必須根據性能、成本、功耗、尺寸等目標,確定封裝形式(如QFP、BGA、SiP等)。芯片的引腳定義、電源/地網絡規劃、高速信號線的布局,都必須與封裝的引腳排布、層疊結構、布線能力相匹配。現代的高性能芯片(如CPU、GPU)普遍采用“芯片-封裝協同設計”流程,通過仿真工具在早期評估封裝對信號、電源完整性和熱性能的影響,避免設計完成后因封裝限制導致性能不達標。

- 封裝技術推動設計架構演進:封裝技術的進步直接擴展了芯片設計的能力邊界。例如,通過2.5D/3D先進封裝(如硅中介層、TSV硅通孔技術),可以將多個不同工藝、不同功能的裸片(如邏輯芯片、高帶寬內存HBM)集成在一個封裝體內,形成“異構集成”系統。這使得設計者能夠突破單芯片在面積、功能和內存帶寬上的限制,無需將所有功能都擠進單一工藝的巨型裸片中,從而實現了更優的性能、功耗和成本平衡。可以說,封裝已成為實現“超越摩爾定律”的重要路徑。

- 設計決定封裝復雜度:芯片的晶體管數量、I/O引腳數量、工作頻率和功耗水平,直接決定了所需封裝的復雜程度。一個擁有數千個引腳、數百瓦功耗的高性能處理器,必然需要采用多層基板、內置熱沉、精密電源網絡的先進封裝方案。

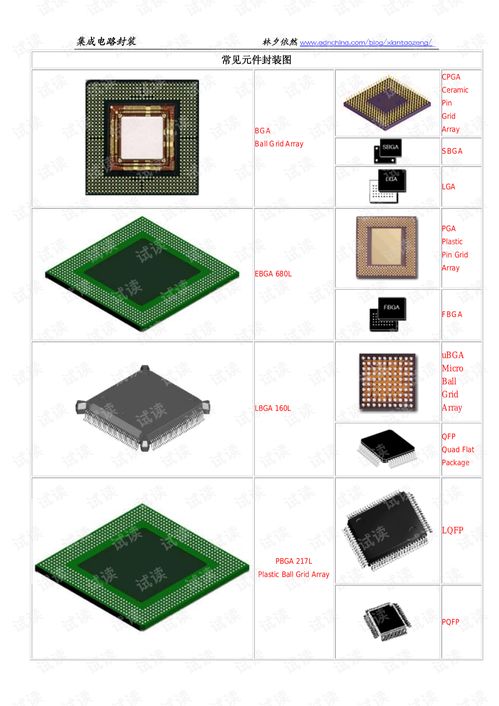

三、 主流封裝技術類型簡介

根據互連方式和集成度,封裝技術主要沿以下路徑發展:

- 通孔插裝型:如雙列直插封裝(DIP),早期常用,現多用于簡單電路。

- 表面貼裝型:如四側引腳扁平封裝(QFP)、球柵陣列封裝(BGA)。BGA因其更高的引腳密度和更好的電氣性能,已成為主流封裝形式之一。

- 芯片級封裝:封裝尺寸與裸片尺寸近乎相同,如晶圓級芯片尺寸封裝(WLCSP),極大減小了體積。

- 系統級封裝:將多個裸片和無源元件集成于同一封裝內,形成一個功能完整的子系統或系統。

- 2.5D/3D集成:通過硅中介層或TSV技術,在垂直方向堆疊多個裸片,實現極高的互連密度和帶寬,是當前高端計算和人工智能芯片的關鍵技術。

結論

集成電路封裝是芯片從設計圖紙走向實用產品的橋梁,是保障其性能、可靠性與可用性的關鍵環節。它與集成電路設計不再是簡單的先后關系,而是貫穿產品開發全周期的、緊密互動的共生關系。隨著半導體技術向更小節點和異構集成邁進,封裝技術的創新將扮演越來越重要的角色,與芯片設計共同塑造未來電子系統的形態與能力。

如若轉載,請注明出處:http://www.lazbw.cn/product/58.html

更新時間:2026-02-20 01:03:41